프로세서(processor)란?

컴퓨터 구조에서 프로세서란 컴퓨터 운영을 위해 기본적인 명령어들을 처리하고 반응하기 위한 논리회로

CPU Time = Instruction count * CPI * Clock cycle time

- instruction count는 ISA와 compiler에 의해 결정

- CPI와 clock cycle time은 CPU hardware에 의해 결정되므로 CPU 하드웨어가 어떻게 되어있냐에 따라 CPU 성능에 큰 영향

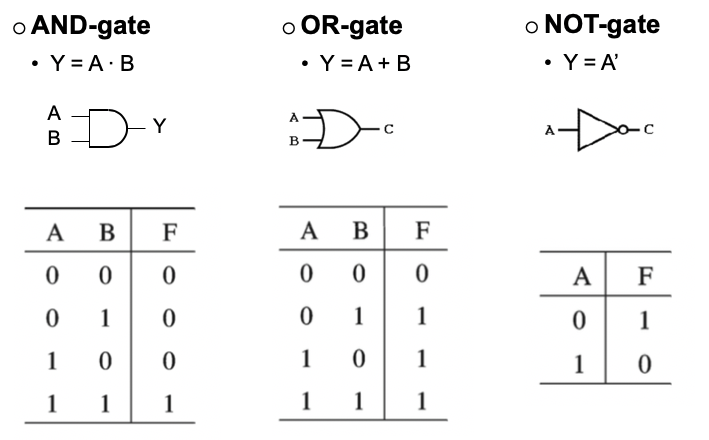

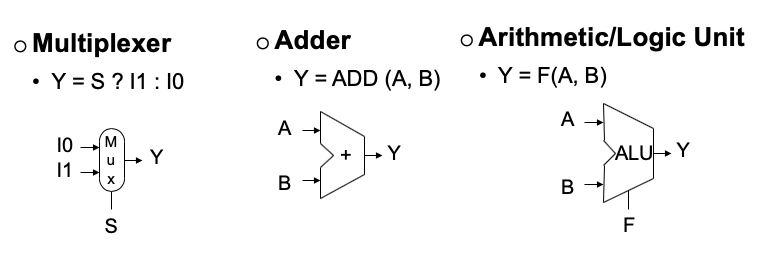

Logic Design Bascis

- 하드웨어는 logic gate(AND, OR, NOT, NAND, NOR, XOR..)라는 simple building block으로 구성됨

- logic은 두가지 타입(조합 논리, 순차 논리)으로 구성

1) Combination circuit(조합 논리)

- input에 의해서 output 결정

- 내부에 저장 요소(storage element)가 존재하지 않음. 즉, 현재 state를 저장 불가능

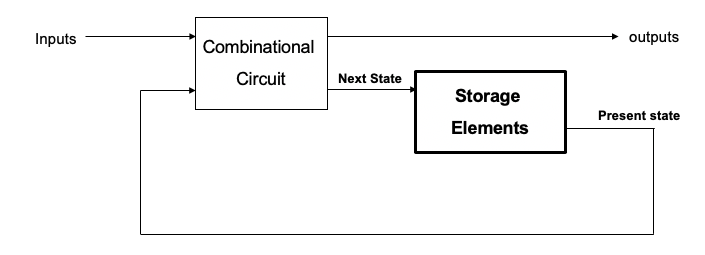

2) Sequential circuit(순차 논리)

- input과 present state에 의해서 output 결정

- 내부에 저장 요소(storage element : binary data를 저장할 수 있는 회로)가 존재

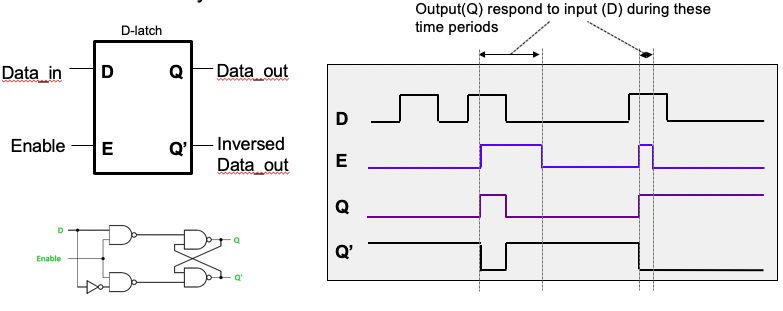

- 저장 요소(storage element)는 latch와 flip-flop이 있음.

(1) latch

- 입력이 변경되는 순간 출력이 변경됨

- 비동기 회로(asynchronous circuit)에 사용

(2) filp-flop

- clock edge에서 값이 변경됨

- 동기 회로(synchronous circuit)에 사용

- n-bit register에는 n개의 플립플롭으로 구성

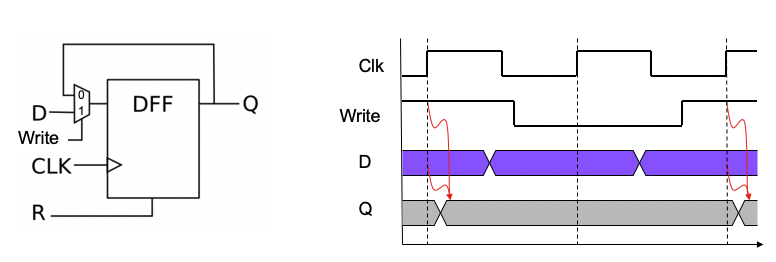

(3) filp-flop with write control

- 플립플롭에 write signal을 추가하여 클럭 엣지이면서 write signal이 1일 때만 값이 변경됨

- 저장값이 선택적으로 또는 나중에 update하기위해 사용

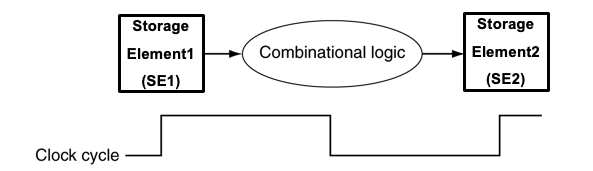

(4) 동기식 회로에서의 clocking methodology

- 조합 회로에서 데이터는 1 클락 사이클 동안 전송됨

- 따라서 클락 엣지에서 이전 storage element에서 다음 storage element로 데이터를 전달함

- 조합회로 중 가장 긴 지연시간이 clock period를 결정(cirtical path)

'CS > Computer Architecture' 카테고리의 다른 글

| Language of the Computer (0) | 2019.12.23 |

|---|---|

| Computer Abstraction and Technology (1) | 2019.12.22 |

| Processor - Datapath (0) | 2019.12.17 |

| Memory Hierarchy (0) | 2019.12.16 |

| Floating Point Number (0) | 2019.12.15 |

댓글